Universidade Estadual de Feira de Santana (UEFS)

Disciplina: Sistemas Digitais (TEC499) - 2025.2

Equipe: Luis Felipe Carneiro Pimentel e Walace de Jesus Venas

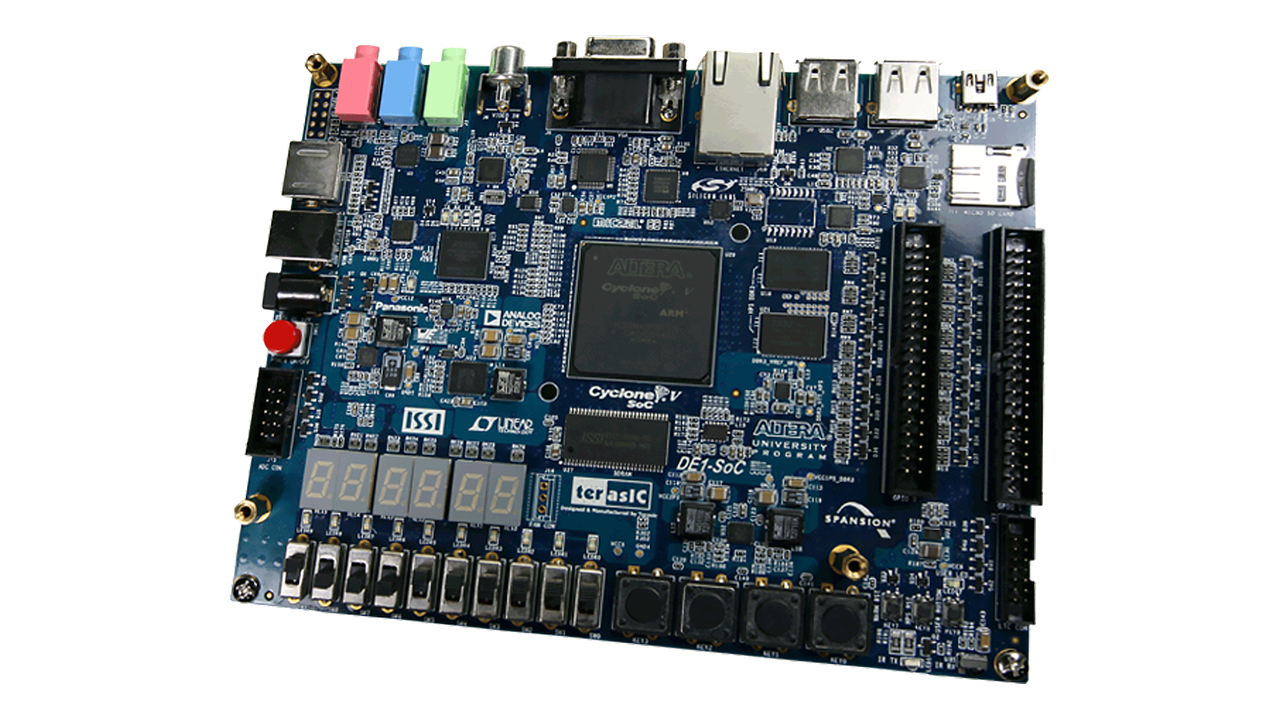

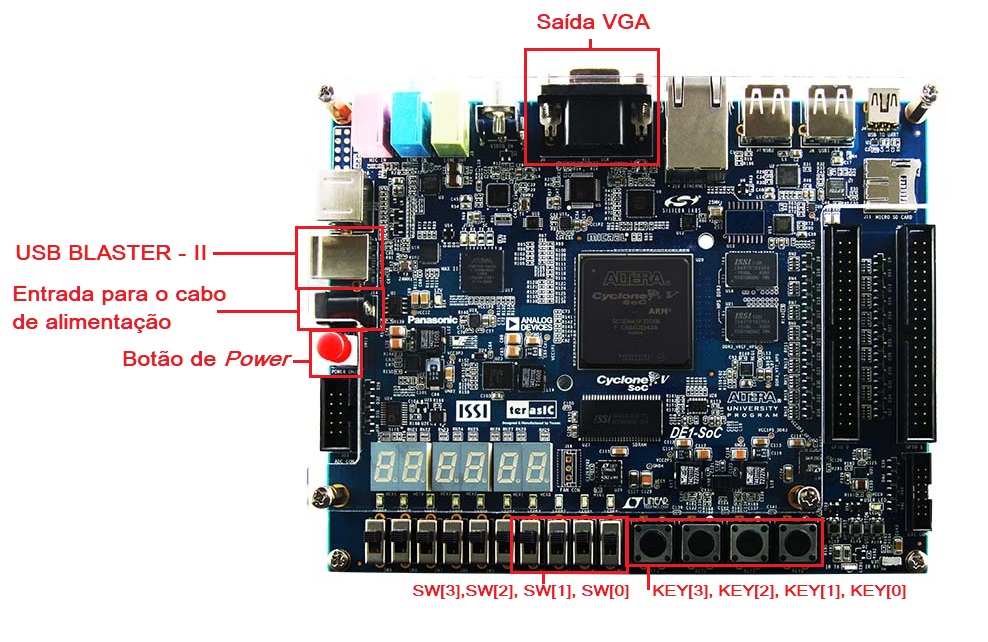

Para a elaboração do projeto, foi utilizado o kit de desenvolvimento DE1-SoC com o processador Cyclone V, permitindo a leitura e escrita de dados diretamente na memória RAM do dispositivo, o ambiente de desenvolvimento utilizado foi o Quartus Lite na versão 23.1 e para linguagem de descrição de hardware foi lidado com Verilog. O objetivo do problema é projetar um módulo embarcado de redimensionamento de imagens para sistemas de vigilância e exibição em tempo real, o hardware deve aplicar o efeito de zoom-in (Ampliação) e zoom-out (Redução) simulando um comportamento básico de interpolação.

- 1. Levantamento de Requisitos

- 2. Softwares Utilizados

- 3. Hardware Usado nos Testes

- 4. Instalação e Configuração

- 5. Testes de Funcionamento

- 6. Análise dos Resultados

- RF01: O sistema deve implementar quatro algoritmos distintos de redimensionamento de imagem.

- RF02: Dois algoritmos devem ser para ampliação (Zoom In): Vizinho Mais Próximo e Replicação de Pixel.

- RF03: Dois algoritmos devem ser para redução (Zoom Out): Decimação e Média de Blocos.

- RF04: Todas as operações de zoom devem ser aplicadas em passos de 2X.

- RF05: A seleção do algoritmo deve ser feita através de chaves físicas (SW) na placa.

- RF06: O controle do nível de zoom (ampliar, reduzir, voltar ao estado anterior) deve ser feito através de botões físicos (KEY).

- RF07: A imagem original deve ser exibida na tela assim que o sistema é ligado.

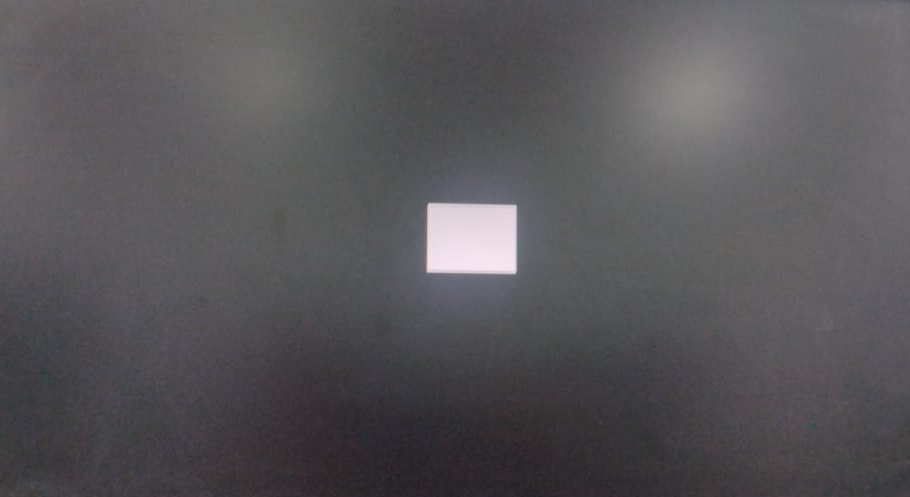

- RF08: A imagem processada deve ser exibida numa saída de vídeo VGA padrão (640x480).

- RF09: O sistema deve fornecer feedback visual ao utilizador através dos displays de 7 segmentos.

- RF10: O sistema deve implementar validações para impedir operações inválidas.

- RNF01: O projeto deve ser desenvolvido inteiramente em linguagem Verilog (2001).

- RNF02: A implementação deve utilizar apenas os recursos de hardware disponíveis na placa DE1-SoC.

- RNF03: O código deve ser modular, bem organizado e detalhadamente comentado.

- IDE de Desenvolvimento: Intel Quartus Prime Lite Edition (23.1std.0)

- Simulador: ModelSim - Intel FPGA Edition (2020.1)

- Linguagem HDL: Verilog-2001

- Placa de Desenvolvimento: Terasic DE1-SoC

- FPGA: Intel Cyclone V SE 5CSEMA5F31C6N

- Memória da Imagem Original: ROM (19.200 palavras x 8 bits)

- Memória de Vídeo (Frame Buffer): RAM de dupla porta (307.200 palavras x 8 bits)

- Monitor: Philips VGA (640x480 @ 60Hz)

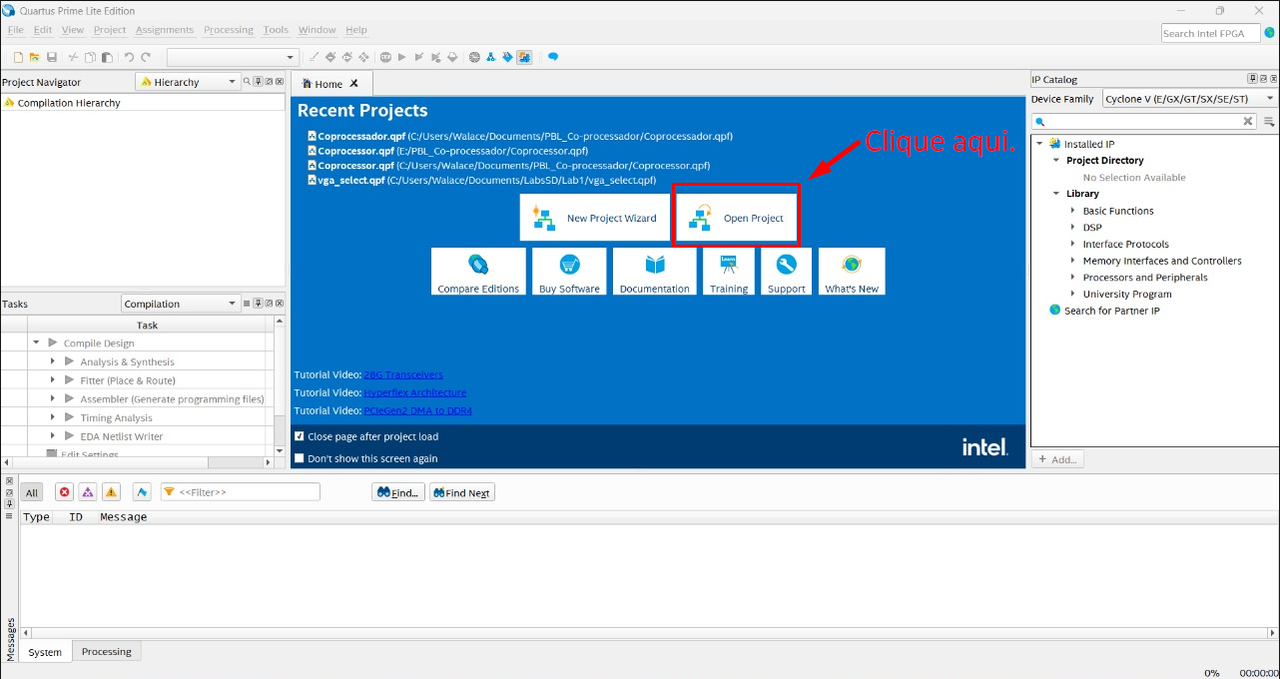

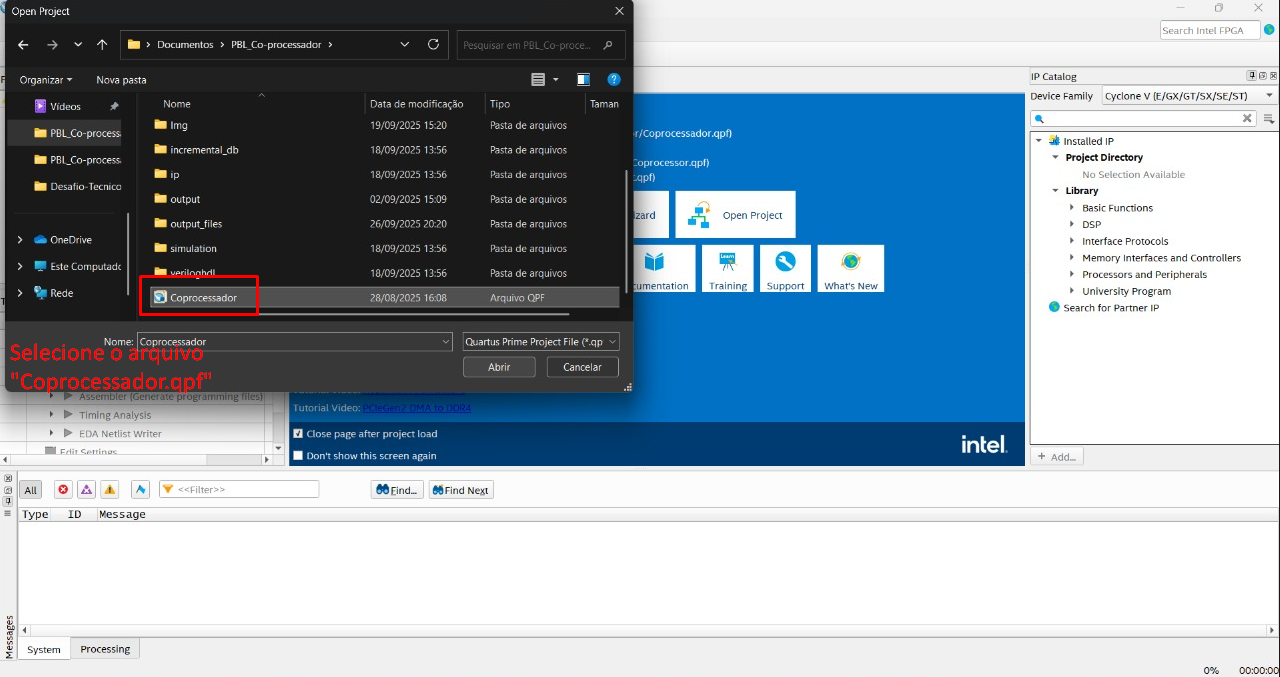

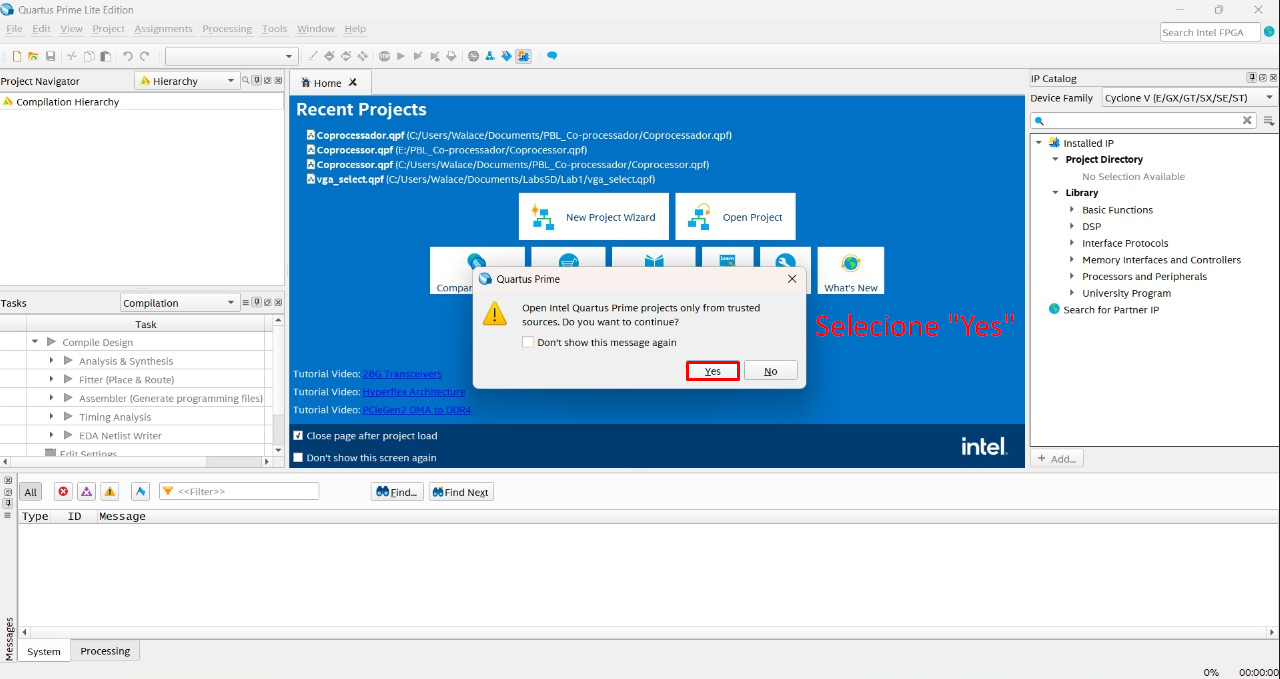

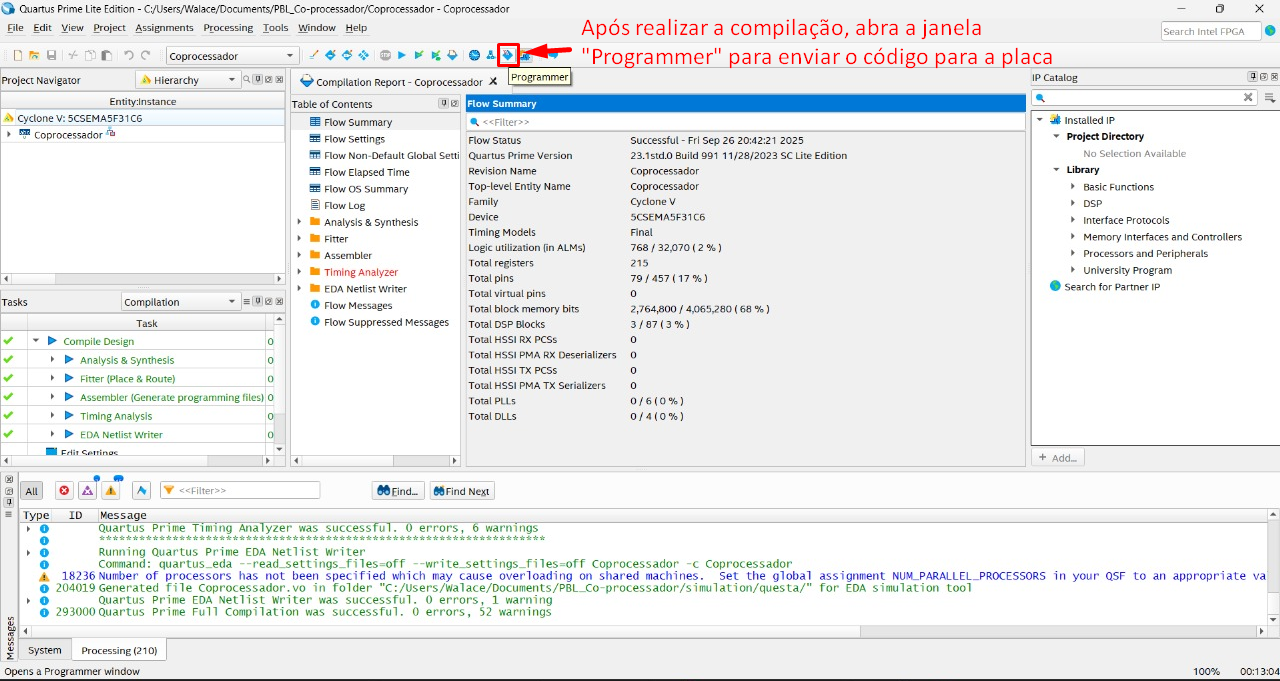

Essa subseção vai explicar o passo a passo para realizar a compilação do projeto no Intel Quartus Prime. A seção vai apresentar informações por texto e uma seção dedicada com imagens para ilustrar o processo de compilação de maneira mais intuitiva.

Após realizar o download do projeto abra o ficheiro Coprocessador.qpf no Intel Quartus Prime.

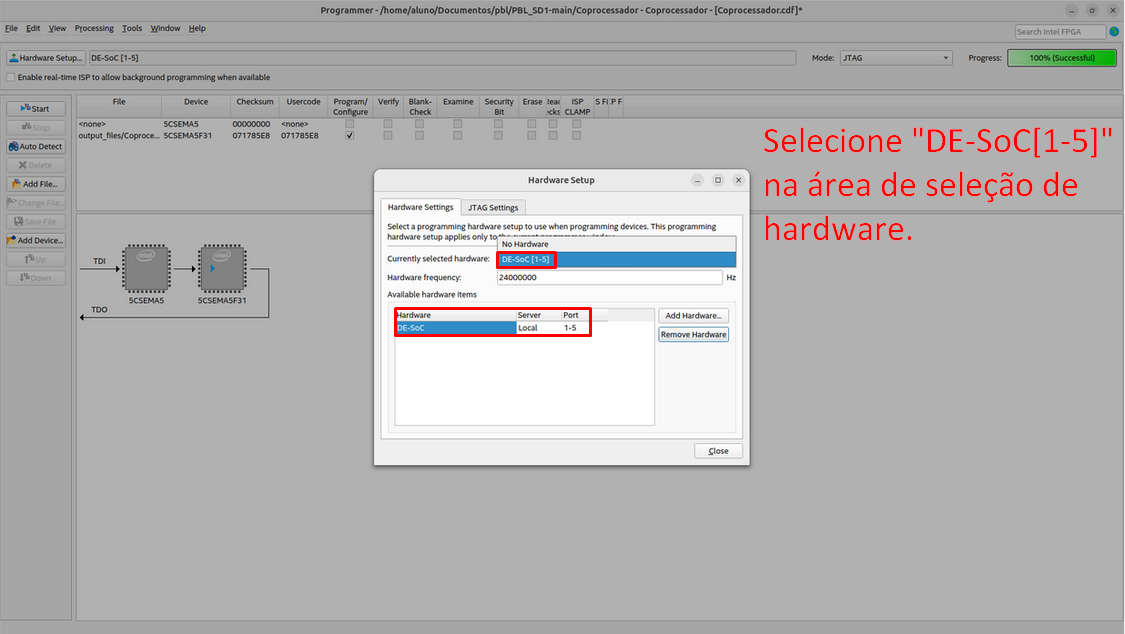

Após a seleção do ficheiro, selecionar DE-SOC na janela de seleção de hardware.

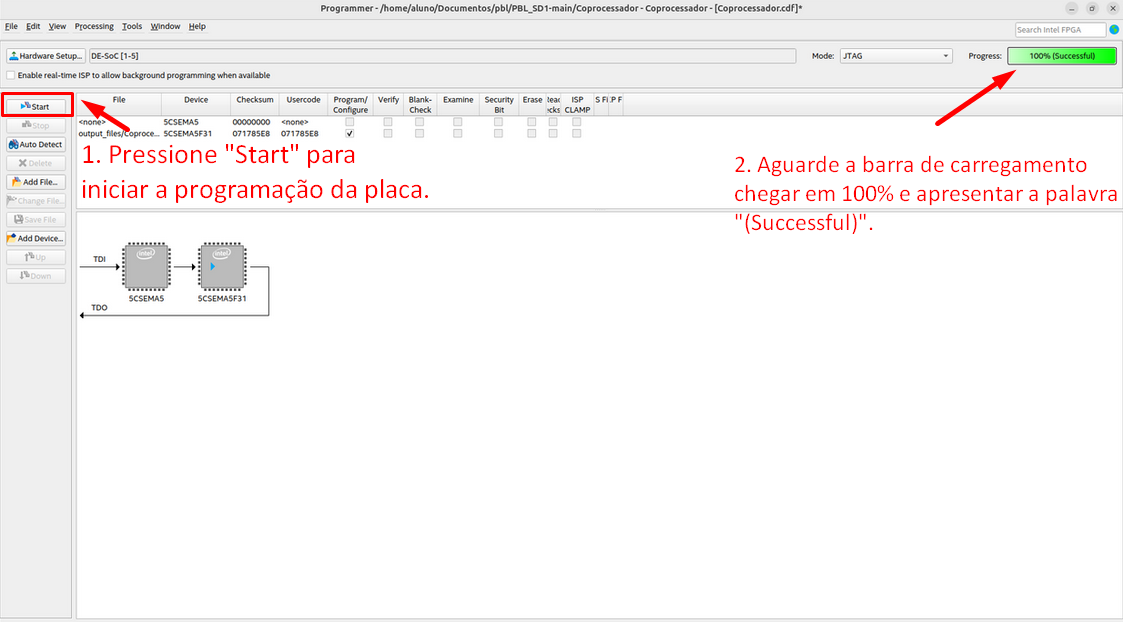

Ao realizar as etapas, pressionar start e aguardar a barra de carregamento chegar em 100%, exibindo a mensagem "Successful".

- Use a ferramenta IP Catalog para gerar os componentes de memória:

- ImgRom.qip → configurado como ROM: 1-PORT com 19200 pixels de 8 bits, inicializado com o ficheiro

.mifgerado na conversão de imagem. - VdRam.qip → configurada como RAM: 2-PORT com 307.200 palavras de 8 bits.

- ImgRom.qip → configurado como ROM: 1-PORT com 19200 pixels de 8 bits, inicializado com o ficheiro

Note

Não é necessário gerar novas memórias caso todos os arquivos do projetos sejam baixados, já que essas memórias já foram geradas.

É crucial configurar cada IP corretamente para evitar erros de compilação.

- Abra o Pin Planner:

Assignments > Pin Planner. - Atribua as portas do módulo

Coprocessadoraos pinos físicos da placa DE1-SoC, conforme a documentação da placa.

Note

Não há necessidade de realizar a atribuição de pinos caso todos os arquivos do projetos sejam baixados, já que, a atribuição de pinos já foi realizada.

- No menu, selecione Processing > Start Compilation.

- Aguarde a síntese, mapeamento, fitting e geração do bitstream.

- Após a compilação bem-sucedida, abra a ferramenta Programmer.

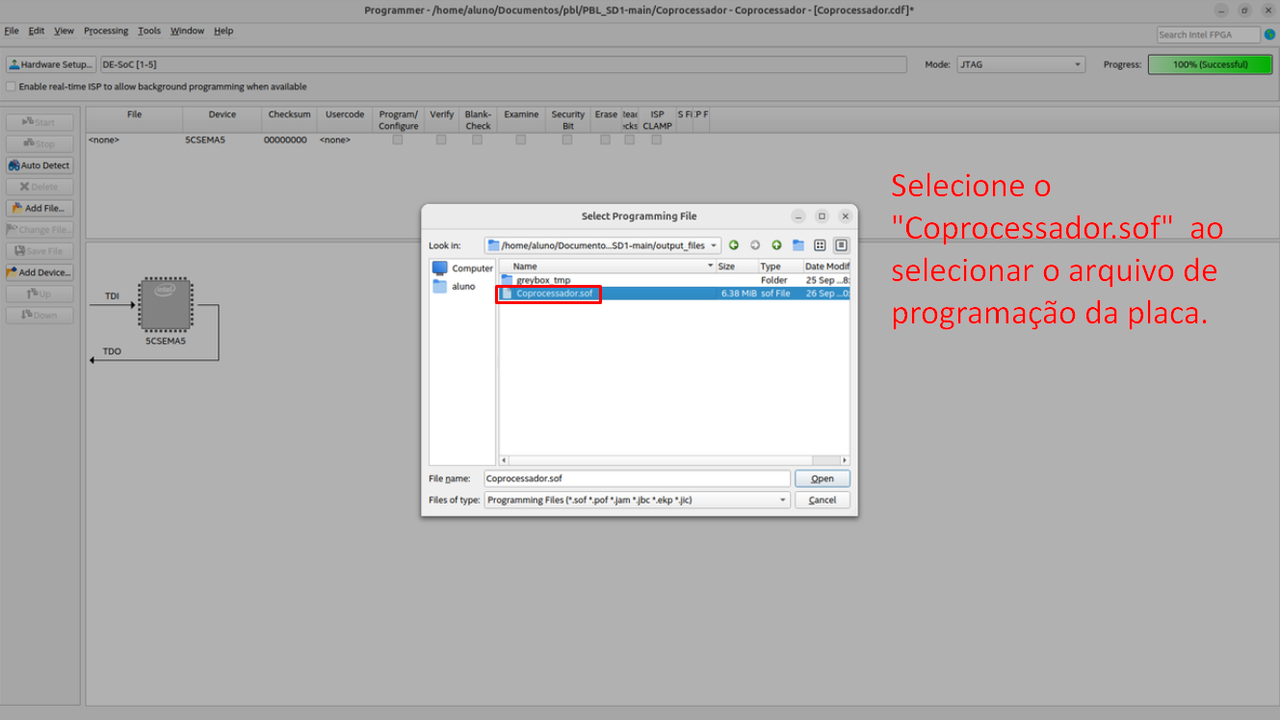

- Carregue o ficheiro

.soflocalizado na pastaoutput_files/. - Clique em Start para programar a FPGA.

- Após fazer a conexão dos cabos de alimentação, VGA e USB, ligar a DE1-SOC pelo botão de Power.

- Esperar o Display de sete segmentos exibir uma mensagem de "SELECT AN ALGORITHM" ou esperar a imagem ser exibida no monitor.

- Selecionar um algoritmo de redimensionamento pelos os Switches da placa. (Do SW[0] até o SW[3], à seleção fonrece os algoritmos Nearest Neighbor, Pixel Replication, Decimation e Block Averaging respectivamente.

- Fazer uso dos botões KEY[2] e KEY[3] para aplicar o redimensionamento da imagem. Vale ressaltar que, KEY[2] é responsável em aplicar zoom-out enquanto o KEY[3] aplica o zoom-in.

- Caso a imagem esteja distorcida ou o usuário queira voltar à imagem original, apertar o botão KEY[0] para reiniciar o sistema e voltar para a imagem original.

| Função | Componente | Descrição |

|---|---|---|

| Reset Geral | KEY[0] | Reinicia o sistema |

| Voltar Zoom | KEY[1] | Reverte para nível anterior |

| Zoom In | KEY[2] | Reduz em 2x |

| Zoom Out | KEY[3] | Amplia em 2x |

| Alg. 1 | SW[0] | Nearest Neighbor |

| Alg. 2 | SW[1] | Pixel Replication |

| Alg. 3 | SW[2] | Decimation |

| Alg. 4 | SW[3] | Block Averaging |

-

Inicialização: O display de 7 segmentos deve mostrar "SELECT AN ALGORITHM".

- Mais de uma chave ligada → display mostra "SELECTION ERROR".

-

Operação de Zoom Válida:

- Com SW[0] ou SW[1], pressione KEY[2] para zoom in (2x → 4x).

- Pressione KEY[3] para reduzir ao nível anterior (2x → 1x).

-

Operação de Zoom Inválida:

- Com SW[2] ou SW[3], pressionar KEY[2] não deve alterar a imagem.

- Display mostra "INVALID ZOOM".

-

Botão Reset: Após qualquer operação de zoom, pressione KEY[0] para retornar ao nível normal.

Warning

KEY[1] no produto final não teve um pino atribuido, ou seja, devido à isso, ao pressionar o botão o nível de zoom não retorna ao normal. Entretanto, a lógica para o funcionamento dele ainda está presente no Verilog do projeto, sendo possível fazer com que o botão volte a ter sua funcionalidade após um pino seja atribuido à ele.

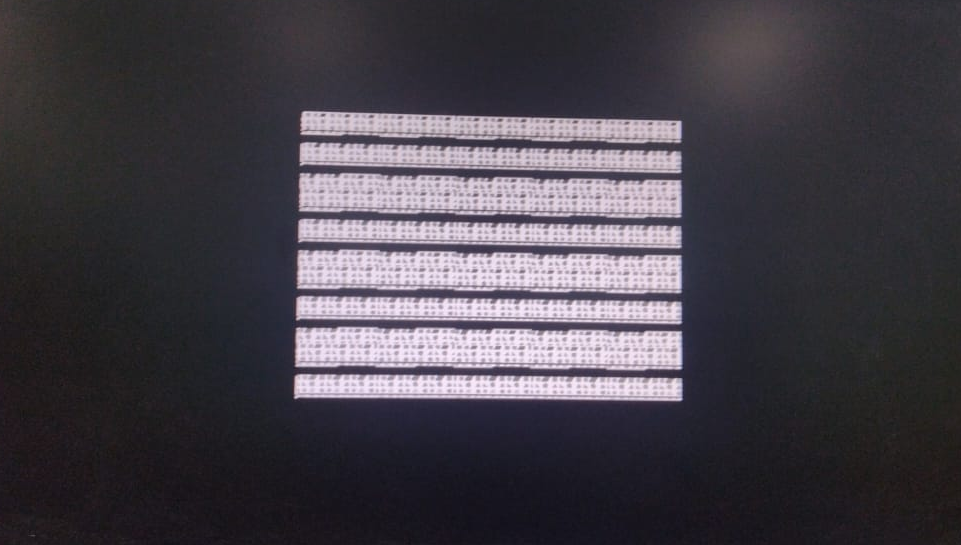

O projeto implementado foi implementado com as seguintes funcionalidades:

- Suporte a 4 algoritmos de redimensionamento.

- Níveis de zoom de 0.25x a 4.0x.

- Interface robusta com feedback em display de 7 segmentos.

- Disponibilização de uma imagem para realizar redimensionamento.

Porém, determinados erros e limitações permaneceram na entrega da etapa 1 do produto:

- Alteração entre algoritmos de zoom causa uma distorção severa à imagem, tornado-se necessário fazer uso do botão de Reset para evitar isso.

- Todos os algoritmos de zoom distorcem a imagem em certo grau.

- O zoom da placa apenas realiza o redimensionamento em 2 etapas cada, ampliando e afastando a imagem duas vezes.

Durante o desenvolvimento do projeto os algoritmos de zoom causam uma distorção da imagem caso a imagem tenha o zoom-in acionado até o máximo (4x) e depois receba um zoom-out. O mesmo acontece com a ordem das ações invertidas, ou seja, caso o usuário acione o zoom-out até o máximo (0.25) e depois tente dar zoom-in na imagem. O problema pode ser evitado caso o usuário decida apertar o botão de "reset" sempre que for testar outro algoritmo de redimensionamento.

Uma possível futura solução para esse problema é a implementação de um "reset automático" que é ativado sempre que o usuário troca de algoritmo enquanto a imagem está fora do seu estado padrão (1x), limitando o usuário a sempre trabalhar com a imagem padrão ao tentar redimensionar com outro tipo de algoritmo.

Ainda seguindo o desafio da distorção de cada zoom, é importante ressaltar que eles são limitados em realizar zoom-in e zoom-out de 2 etapas cada. Ou seja, para uma futura versão do projeto, uma possível melhora seria a remoção dessa limitação imposta, permitindo com que o usuário amplie ou afaste a imagem quantas vezes necessárias.

ALAM, S. Nearest Neighbor Interpolation Algorithm in Matlab. GeeksforGeeks, [S.l.], [s.d.]. Disponível em: https://www.geeksforgeeks.org/software-engineering/nearest-neighbor-interpolation-algorithm-in-matlab/. Acesso em 06 de Setembro.

TUTORIALSPOINT. Zooming Methods in Digital Image Processing. TutorialsPoint, [S.l.], [s.d.]. Disponível em: https://www.tutorialspoint.com/dip/zooming_methods.htm. Acesso em 06 de Setembro.

VISION BOOK MIT. Upsampling and Downsampling. Vision Book MIT, [S.l.], [s.d.]. Disponível em: https://visionbook.mit.edu/upsamplig_downsampling_2.html. Acesso em 06 de Setembro.

COMPUPHASE. Scaling/Zooming of Bitmaps. CompuPhase, [S.l.], [s.d.]. Disponível em: https://www.compuphase.com/graphic/scale2.htm. Acesso em 08 de Setembro.

COMPUPHASE. Scaling/Zooming of Bitmaps (Part 2). CompuPhase, [S.l.], [s.d.]. Disponível em: https://www.compuphase.com/graphic/scale3.htm. Acesso em 08 de Setembro.

SUTHERLAND, S. Verilog-2001: The New Features Part 1. Sutherland-HDL, [S.l.], 2001. Disponível em: https://sutherland-hdl.com/papers/2001-Wescon-tutorial_using_Verilog-2001_part1.pdf. Acesso em 02 de Setembro.

GURU99. Co-processor in Computer Architecture. GeeksforGeeks, [S.l.], [s.d.]. Disponível em: https://www.geeksforgeeks.org/computer-organization-architecture/co-processor-computer-architecture/. Acesso em 27 de Agosto.

ALAM, S. Introduction of Control Unit and its Design. GeeksforGeeks, [S.l.], [s.d.]. Disponível em: https://www.geeksforgeeks.org/computer-organization-architecture/introduction-of-control-unit-and-its-design/. Acesso em 30 de Agosto.